- 您现在的位置:买卖IC网 > Sheet目录362799 > EVAL-AD1870EB (Analog Devices, Inc.) Single-Supply 16-Bit Stereo ADC

AD1870

REV. A

–

16

–

BCLK

RDEDGE = LO

OUTPUT

BCLK

RDEDGE = HI

31

32

1

2

3

16

SOUT

OUTPUT

WCLK

OUTPUT

TAG

OUTPUT

LSB

LEFT TAG

MSB

LSB

RIGHT TAG

MSB

31

32

1

2

3

16

MSB-1

LEFT DATA

MSB-2

LSB

MSB-1

RIGHT DATA

MSB

MSB-2

LSB

ZEROS

ZEROS

ZEROS

L

R

CK

OUTPUT

17

18

17

18

MSB

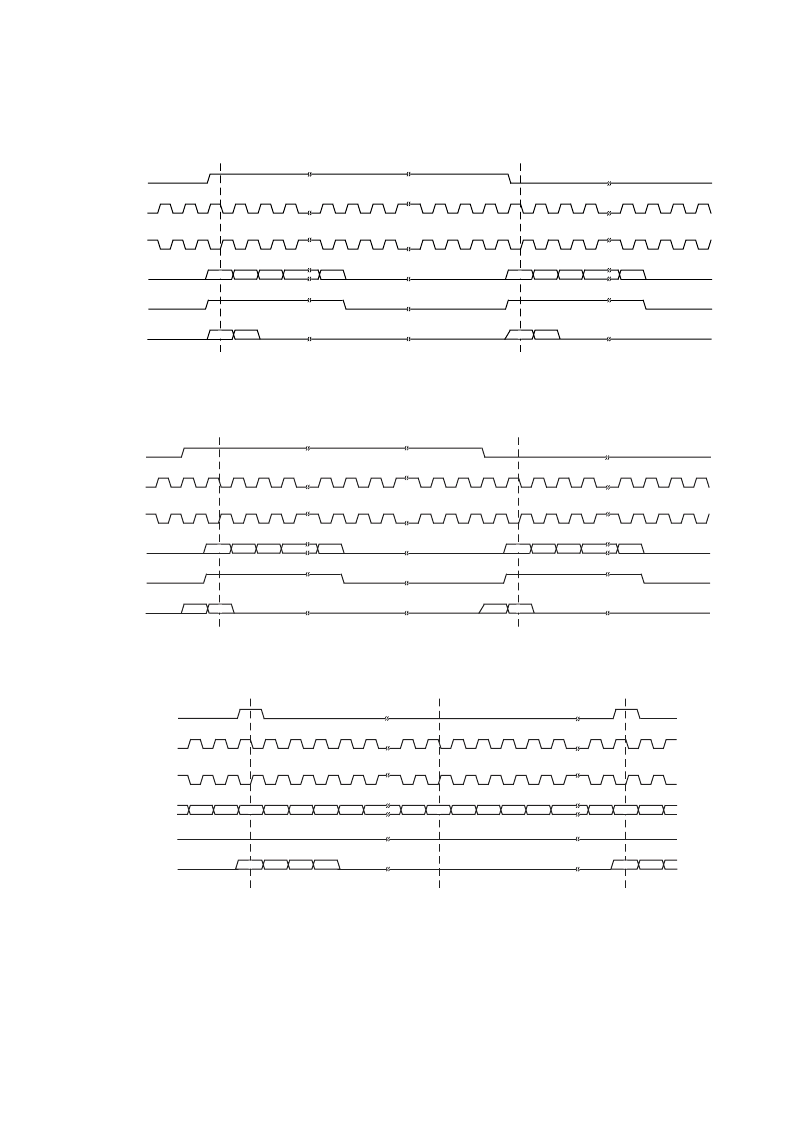

Figure 13. Serial Data Output Timing: Master Mode, Left-Justified with No MSB Delay,

S/

M

= LO, R

L

JUST = LO,

MSBDLY

= Hl

BCLK

RDEDGE = LO

OUTPUT

BCLK

RDEDGE = HI

32

1

2

3

4

17

SOUT

OUTPUT

WCLK

OUTPUT

TAG

OUTPUT

MSB

LEFT TAG

MSB

RIGHT TAG

31

32

1

2

3

4

17

MSB-1

LEFT DATA

MSB-2

LSB

MSB-1

RIGHT DATA

MSB

MSB-2

LSB

ZEROS

ZEROS

ZEROS

L

R

CK

OUTPUT

MSB

LSB

LSB

Figure 14. Serial Data Output Timing: Master Mode, I

2

S-Justified, S/

M

= LO, R

L

JUST = LO,

MSBDLY

= LO

BCLK

RDEDGE = LO

BCLK

RDEDGE = HI

31

32

1

2

3

4

16

SOUT

OUTPUT

WCLK

OUTPUT

TAG

OUTPUT

19

20

21

32

1

2

INPUT

HI

HI

5

17

18

LSB

LEFT TAG

MSB

MSB

LSB

RIGHT TAG

LEFT TAG

LSB

MSB

MSB-14

LSB

PREVIOUS DATA

MSB-1 MSB-2 MSB-3

LEFT DATA

MSB-4

MSB-3 MSB-4

LSB

MSB-1 MSB-2

RIGHT DATA

LSB

MSB-1

LEFT DATA

MSB

L

R

CK

INPUT

MSB

MSB

Figure 15. Serial Data Output Timing: Slave Mode, Left-Justified with No MSB Delay,

32-Bit Frame Mode, S/

M

= Hl, R

L

JUST = LO,

MSBDLY

= Hl

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-AD1896EB

Automotive Low-Cost Non-Volatile FPGA Family; Voltage: 1.2V; Grade: -5; Package: Lead-Free ftBGA; Pins: 256; Temperature: AUTO; LUTs (k): 8

EVAL-AD1928EBZ

2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1928EB

2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1938EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1939EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1935EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1936EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1937EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

相关代理商/技术参数

EVAL-AD1871EB

制造商:Analog Devices 功能描述:STEREO AUD, 24BIT, 96 KHZ, MULTIBIT- ADC - Bulk

EVAL-AD1871EBZ

功能描述:BOARD EVAL FOR AD1871 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件

EVAL-AD1895EB

制造商:Analog Devices 功能描述:EVAL BD FOR AD1895 192KHZ 8:1 STEREO - Bulk

EVAL-AD1896EB

制造商:Analog Devices 功能描述:Evaluation Kit For 24-Bit, High-Performance, Single-Chip, Second Generation Asynchronous Sample Rate Converter 制造商:Analog Devices 功能描述:EVAL KIT FOR AD1896 7.75:1 TO 1:8, 192KHZ STEREO ASRC EVAL B - Bulk

EVAL-AD1928EB

制造商:AD 制造商全称:Analog Devices 功能描述:2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1928EBZ

制造商:AD 制造商全称:Analog Devices 功能描述:2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1934EB

制造商:AD 制造商全称:Analog Devices 功能描述:8-Channel DAC with PLL, 192 kHz, 24 Bits

EVAL-AD1935EB

制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC